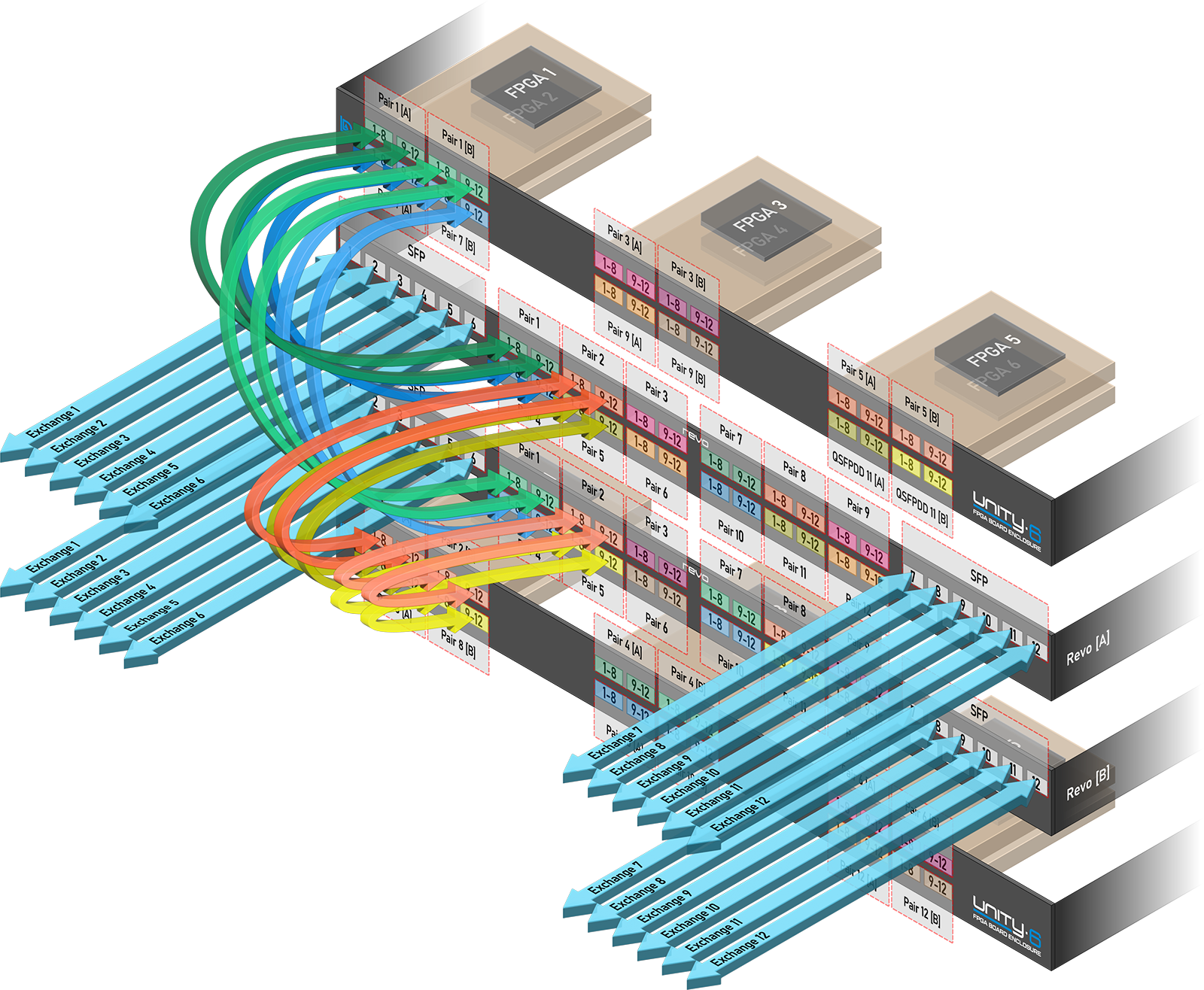

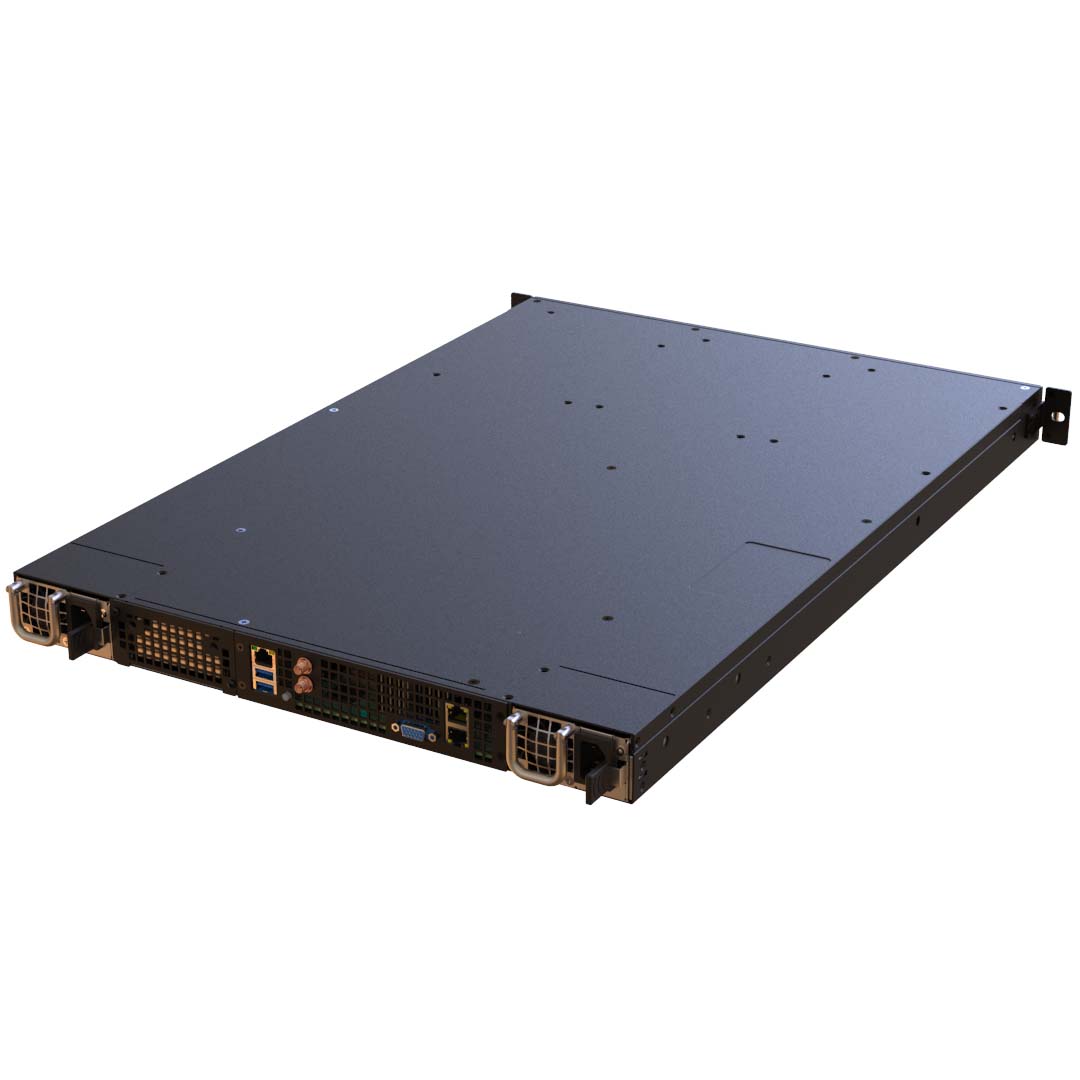

A specialized Layer 1 device designed to make the multi-line arbitration infrastructure "revolutionary" simple, LDA Revo receives and distributes data from multiple exchange lines to multiple downstream devices with a consistent latency of less than 2.6 nanoseconds.

The LDA Revo appliance features:

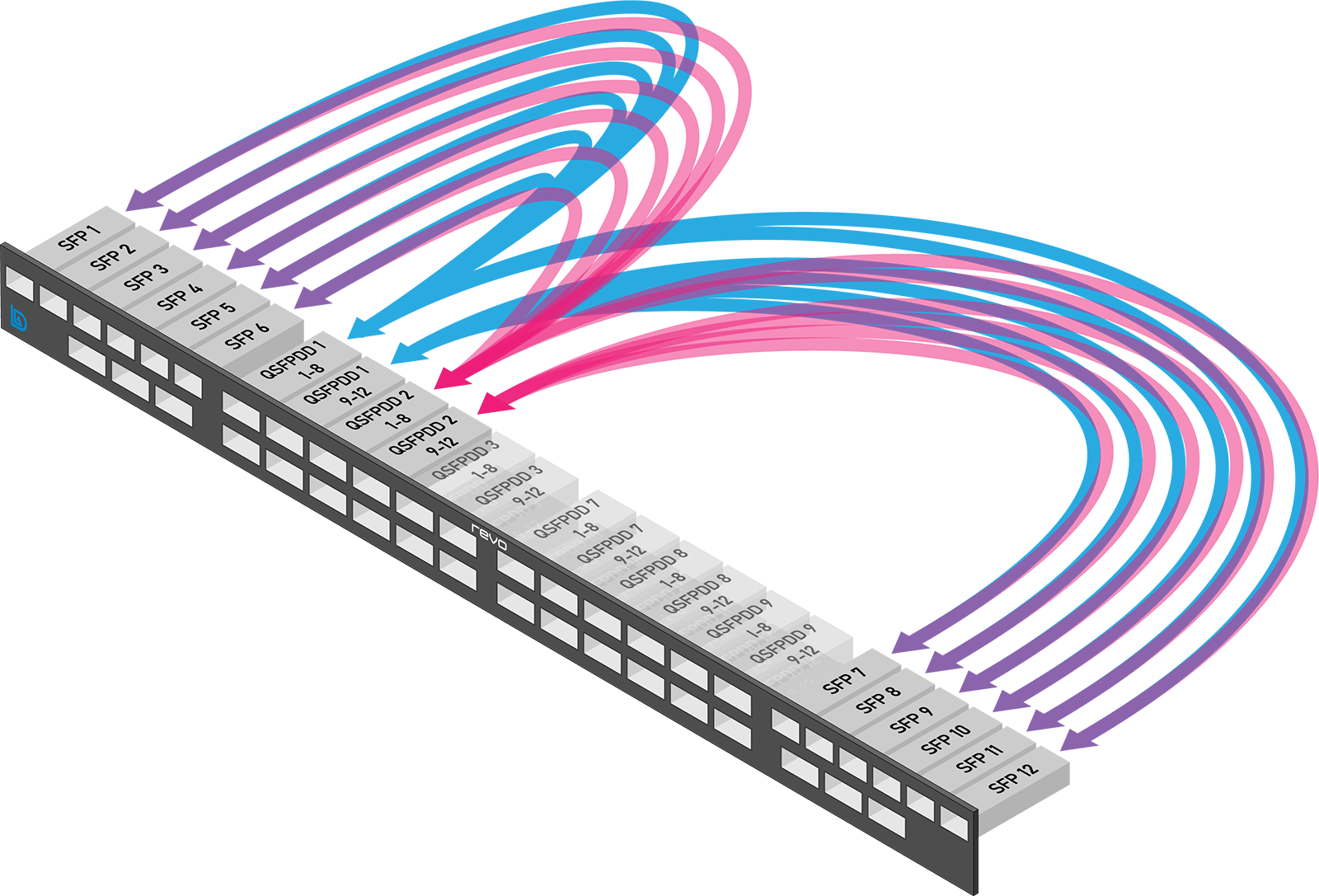

- 12x SFP+ ports for exchange connectivity

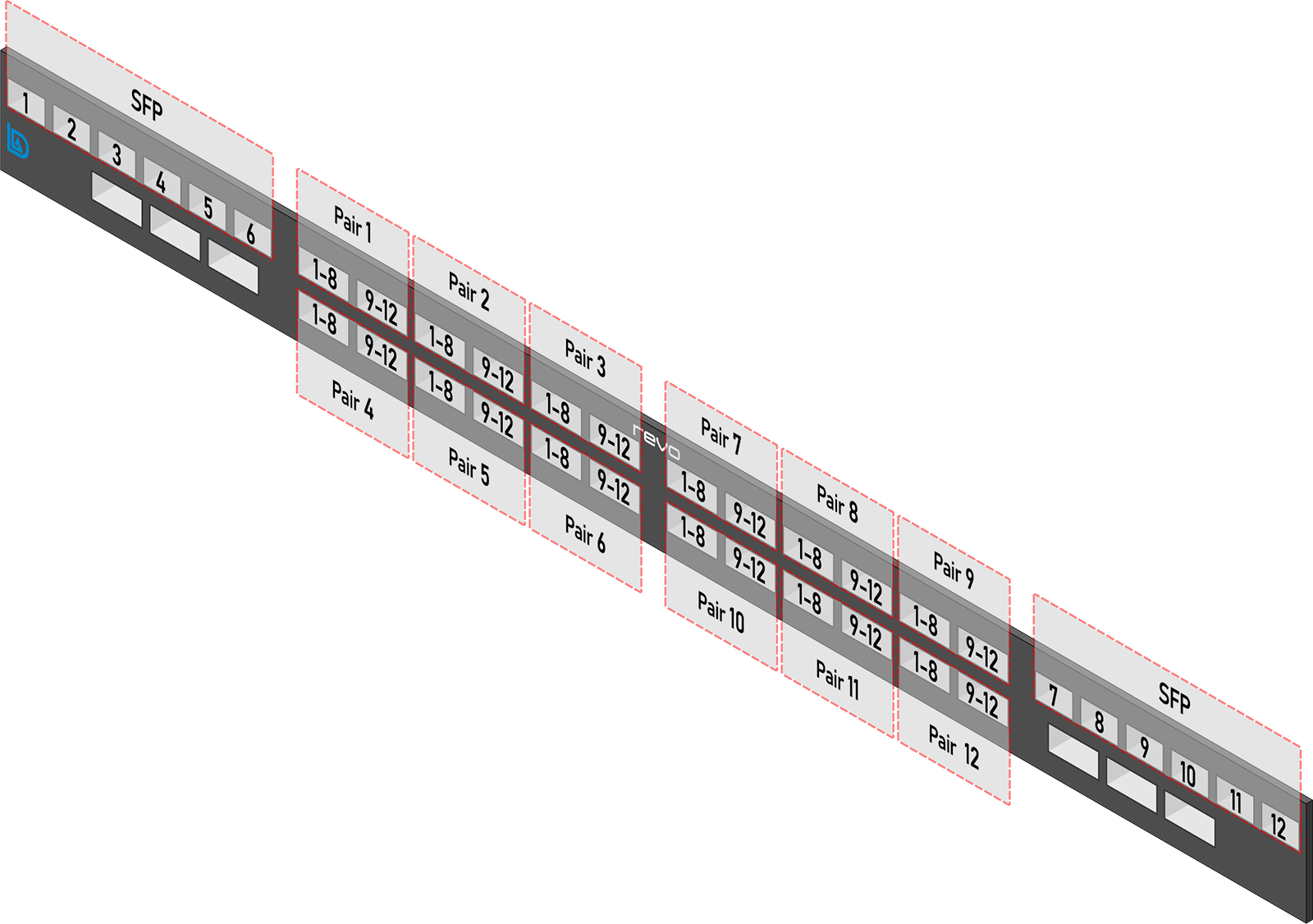

- 24x QSFPDD ports (12 port pairs) for downstream (FPGA board) connectivity

- 6x QSFPDD ports for housekeeping/management tasks or external timestamping/capture

- Configurable Layer 1 for SFP+ output

- Downstream interconnect with 2"-7" QSFPDD copper cables

- Internal tap aggregation and timestamping option with all LDA NeoTap features for capture and monitoring.