Device Connectivity

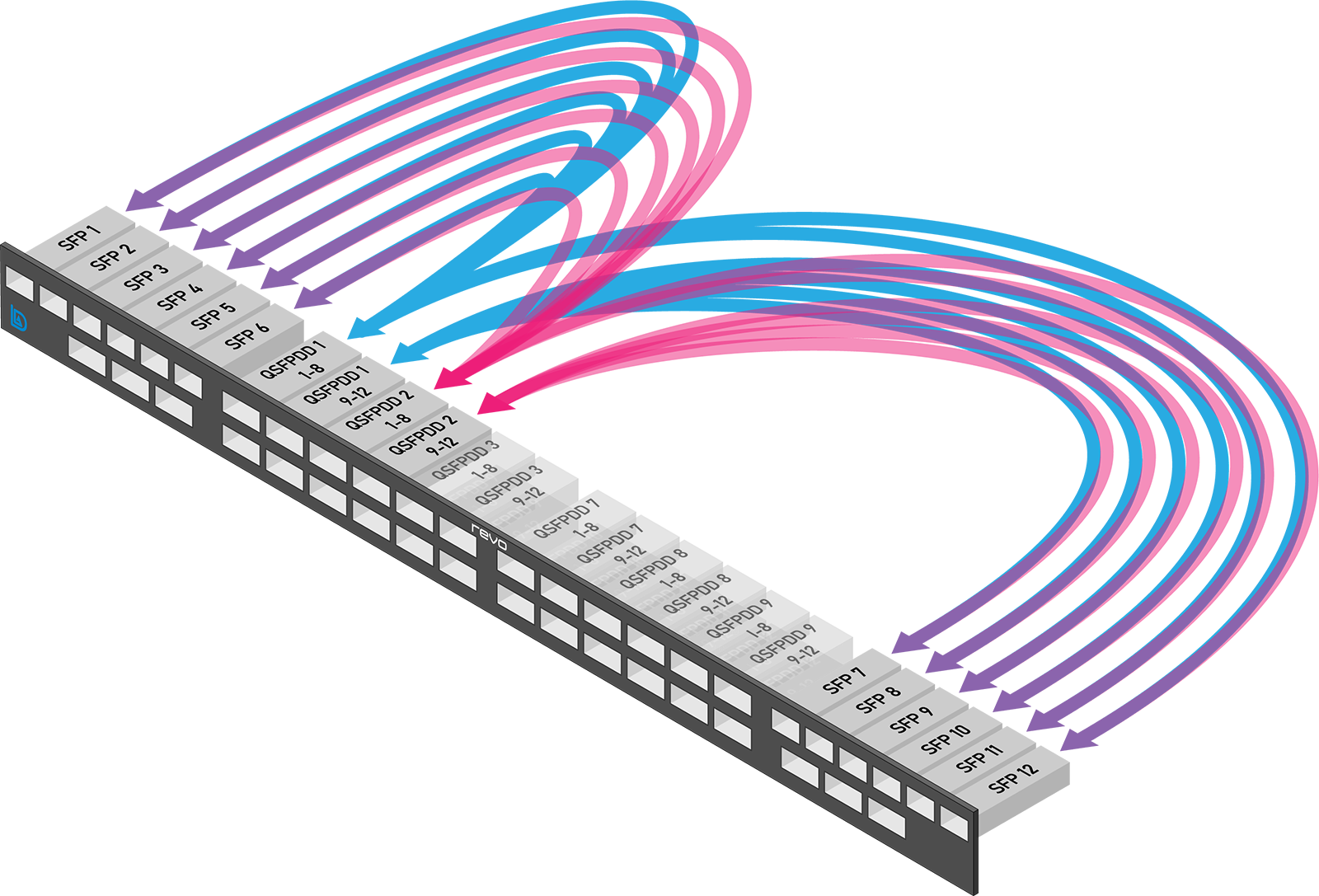

The device's SFP+ ports are strategically distributed in such a way as to be as close as physically possible to the fiber links coming from the exchange. At the same time, QSFPDD ports are grouped in the middle to ensure cables connecting to downstream devices are as short as physically possible.

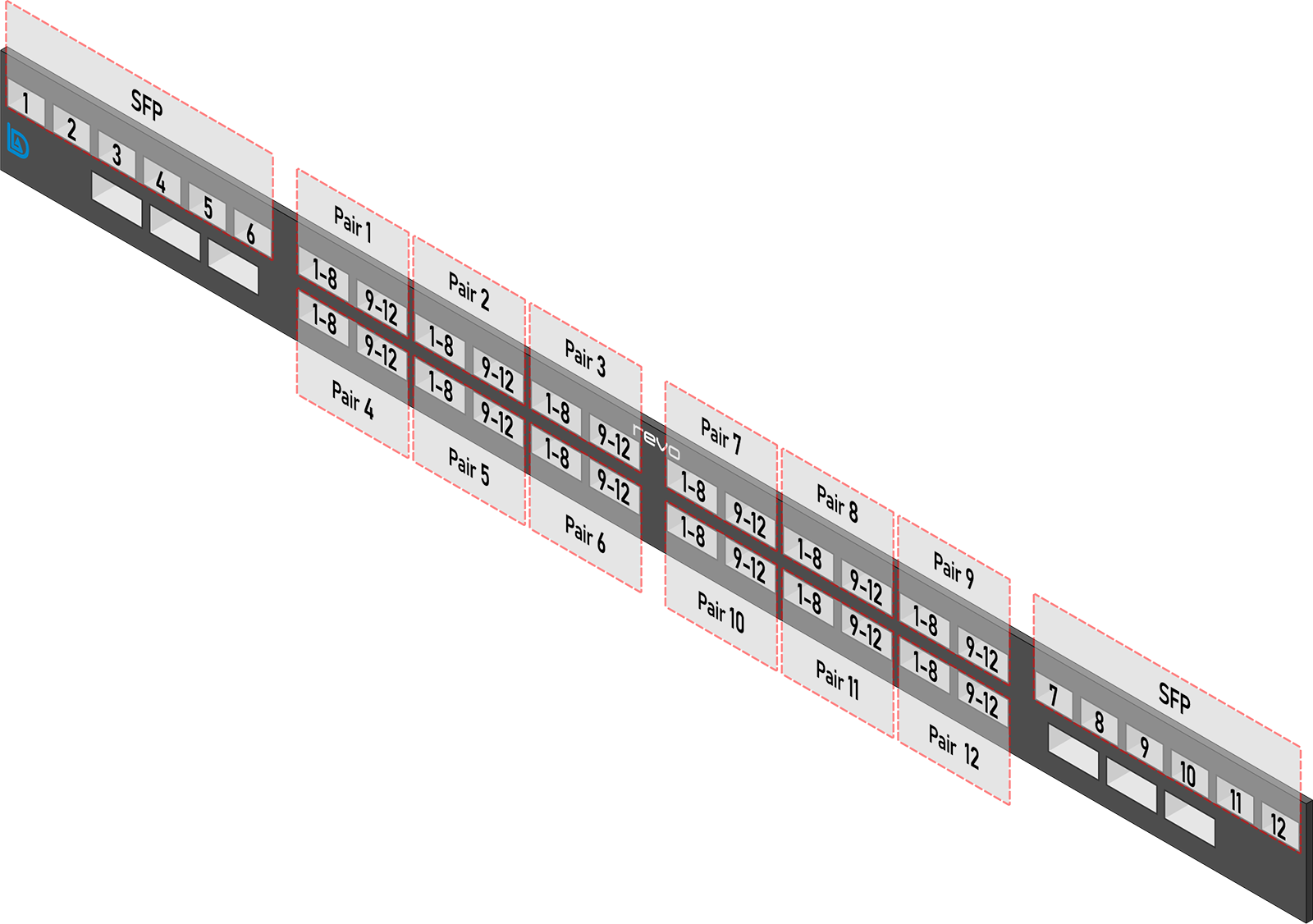

The LDA Revo replicates data (at Layer 1) from 12 SFP+ ports to 12 downstream devices using 24 QSFPDD ports. QSFPDD ports are grouped in pairs, carrying 12 lanes (8+4) per pair, leaving 4 lanes of the second port unused.

Each incoming port connects to a single crosspoint switch providing ultra-low unified latency replication across all ports. LDA's unique approach of splitting replication between multiple smaller crosspoint switches allows for the elimination of any extra latency introduced by larger crosspoint switches and the longer traces needed to deliver data to/from them.

Six auxiliary management QSFPDD ports are intended for tap aggregation/compliance purposes. A copy of each SFP+ lane ingress/egress link is replicated to the management QSFPDD ports.